We don’t live in Woz’s world anymore.

When Steve Wozniak designed the Apple I, he did so almost entirely on his own, hand-wiring the prototype and writing the system software, including a version of BASIC, all within a strikingly short time. Today’s semiconductor development looks nothing like this. Now, the time-to-market (TTM) for semiconductor chips stretches across several years. Further, driving innovation in the industry is not cheap. Broadcom alone spent north of $9 billion on R&D, last year. According to Deloitte, the chip industry spent 52% of earnings before interest and taxes (EBIT) on R&D, in 2024. In fact, R&D seems to be growing at a 12% CAGR, white EBIT is only growing at 10%. These drawn-out timelines don’t just slow innovation—they have severe economic, competitive, and market consequences.

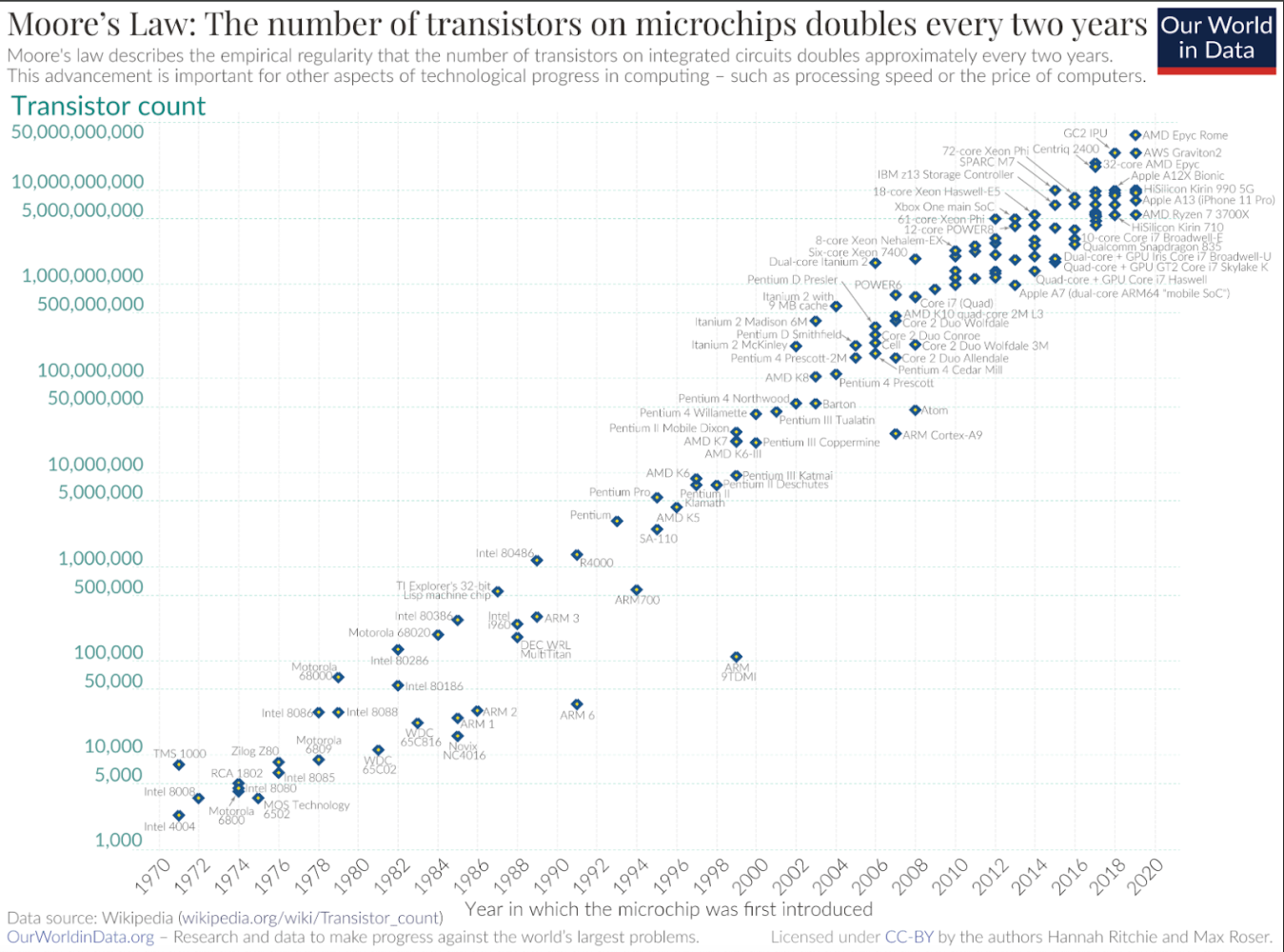

The hidden cost of Moore’s Law is that exponential growth in computing power comes with an exponential increase in development complexity. At the turn of the last century, Intel’s Pentium 4—the cutting-edge CPU for PCs at the time—contained 42 million transistors. Fast forward to today, and high-end processors like Apple’s M3 have upwards of 20 billion transistors. Designing and manufacturing such chips is no small feat. Moving to smaller nodes like 3nm, 2nm and beyond requires precision that involves layers of additional design, testing, and verification.

Chips today undergo multi-stage and serial design processes that involve increasing levels of complexity at each step. From initial architecture to testing and final verification, each phase requires precise execution. As specifications are locked-in up-front, mistakes become exponentially more costly in time and investment as the design moves forward. Each stage introduces risk to the overall convergence of the process; engineers trade off this risk with design margin, impacting the performance, cost, and energy-efficiency of the final outcome. Specialized tools, such as Electronic Design Automation (EDA) software, and cutting-edge lithography techniques like Extreme Ultraviolet (EUV), are crucial for ensuring precision, but they add significant time to the overall process. To finish the design of a chip, multiple EDA software tools are employed, often from multiple vendors. To manage the handoff and to guide the tools, engineers develop software scripts to bind them together. These scripts themselves are sources of costly errors and added time to market delays. In short, there are a lot of places where things can go wrong and the consequences could be dire for the project and the company.

Fabricating advanced chips on the scale of billions of transistors requires flawless precision. Processes like etching and ensuring the structural integrity of silicon wafers have to be exact. Any mistake can lead to costly reworks. The more advanced the chip, the more room for error. As manufacturing processes become more complex, so does the time it takes to bring them to market. The imperfections in design and the edge cases in manufacturing process compatibility can severely affect the production yield of the product, driving up the unit costs and lowering the gross profits. The dilemma is to live with a low yield or fix the issues back in the design files. That is often another $100M dollar question.

The semiconductor supply chain is a deeply interconnected and concentrated ecosystem—any disruption to one part of it can have cascading effects. A small group of companies, such as TSMC, Samsung and GlobalFoundries, dominate chip production, with 5 companies accounting for more than 80% of the world’s supply. According to BCG, a fab completed in 2026 would carry a ten-year total-cost-of-ownership (TCO) of $35 billion to $43 billion. Disruptions, such as material shortages, natural disasters, or geopolitical tensions, slow down production timelines and cause TCO to skyrocket. These delays can take years to resolve, as seen during the pandemic when global chip shortages reverberated across industries.

Before hitting the market, chips must pass various certification processes to ensure they meet regulatory standards. These processes are lengthy and can’t be easily scaled to match increasing demand. Governments are not in the business of expanding regulatory approval capacity exponentially!

Each new generation of chips costs more to develop than the previous, not just due to complexity but also because of variability and unpredictability during development, which often leads to cost overruns. This leaves companies vulnerable to the Innovator’s Dilemma 2.0: being out-innovated before their product even reaches the market.

The rapid pace of technological change means that a chip that takes years to develop risks becoming obsolete by the time it’s ready. If a competitor can bring a newer, more efficient chip to market just a few months earlier, it can capture a significant share of the market. With lengthening development timelines, shaving 5% out of the time-to-market could translate into quarters of competitive advantage. And a missed launch window could mean lost market share that is nigh-impossible to regain. A third place finish in the semiconductor industry is often equivalent to a failed business case outcome.

Long development cycles not only mean a loss of market share but also a reduced ability to innovate quickly. Delayed timelines accumulate across multiple projects, affecting a company’s entire pipeline of innovation - imagine Eli Goldratt’s Herbie showing up in multiple processes at the same time.

Long development cycles not only mean a loss of market share but also a reduced ability to innovate quickly. Delayed timelines accumulate across multiple projects, affecting a company’s entire pipeline of innovation - imagine Eli Goldratt’s Herbie showing up in multiple processes at the same time.

Foundries invest billions into new process technology and production facilities but only start seeing returns once the customers they’re supporting begin production. The long TTM for designing and building chips severely impacts their return on investment. This creates pressure to manage customer expectations while still pushing forward with new technology.

In my recent piece, Semiconductors: An Industry at the Precipice, I discussed how the semiconductor industry is at a critical juncture. With chip design complexities growing and the shortage of skilled designers intensifying, the semiconductor industry must rethink design, fundamentally. In an era when software applications can scale to 100M users in the matter of months or weeks, semiconductors cannot take years to introduce new innovations. “Software is eating the world” was only made possible because it has been more adaptable in the way it employs new ideas and lets go of entrenched practices. The software industry has demonstrated, over the years, the power of creating new value by reusing what others have already built. The standardization of software operating systems like Linux is a great example of this principle, as it means that you don't rebuild bespoke software elements just because you can. A transformational shift in chip design is needed - incremental improvements will no longer suffice. Those who fail to adapt will be left behind by competitors that do. The race to innovate in the semiconductor world is no longer just about speed—it’s about survival.